#### **eMemory** Briefing -

# ememory

#### IPR Notice

All rights, titles and interests contained in this information, texts, images, figures, tables or other files herein, including, but not limited to, its ownership and the intellectual property rights, are reserved to eMemory Technology Incorporated and PUFsecurity Corporation. This information may contain privileged and confidential information. Any and all information provided herein shall not be disclosed, copied, distributed, reproduced or used in whole or in part without prior written permission of eMemory Technology Incorporated or PUFsecurity Corporation.

#### Company Overview

eMemory is the global leader of embedded non-volatile memory IP

# Founded

Based in Hsinchu, Taiwan. IPO in 2011. Over 65M wafers shipped.

#### 1260+ Patents Issued

203 pending patents. 360 employees with 68% R&D personnel.

# Best IP Partner

TSMC Best IP Partner Award since 2010.

#### Technology Portfolio

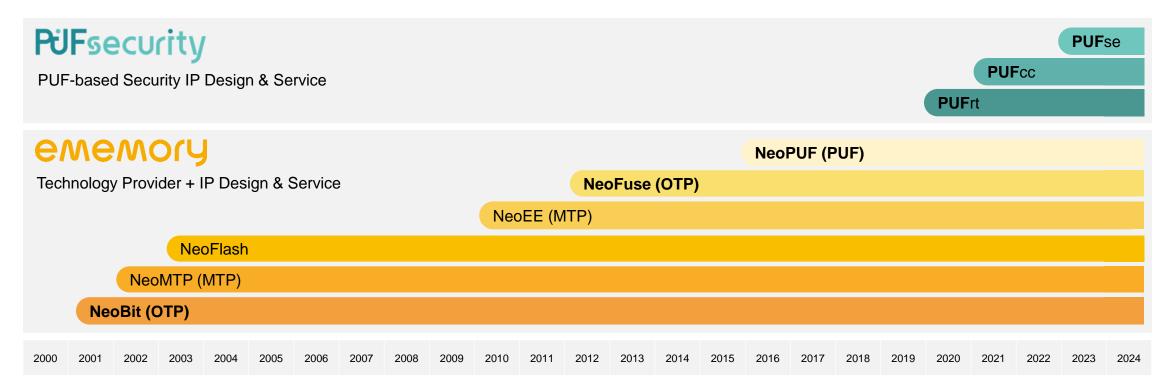

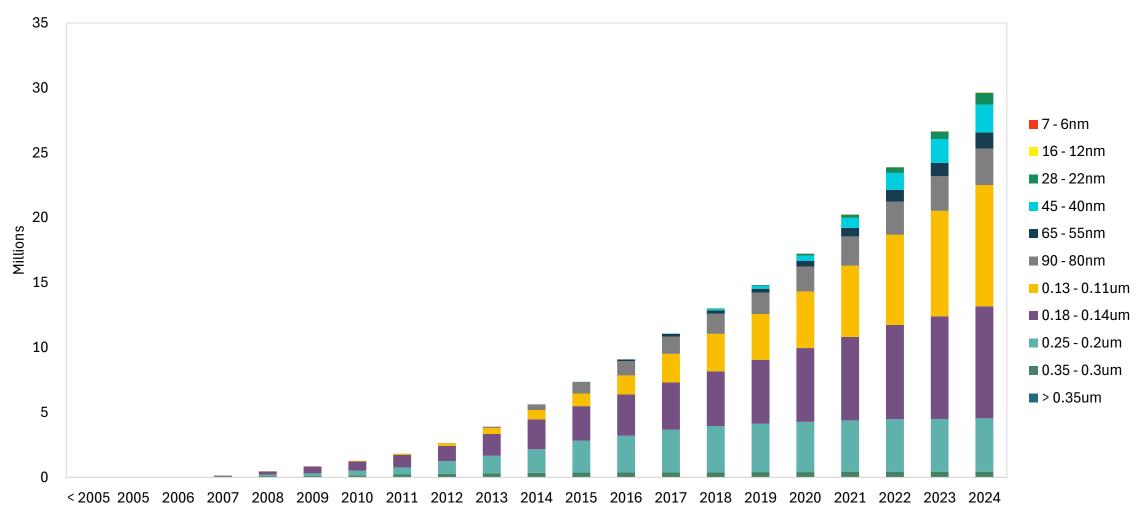

With access to eMemory's widely verified IP process platform, PUFsecurity is uniquely positioned to provide **OTP and PUF-based** Security IP Solutions with **extensive availability** across various foundries and process nodes.

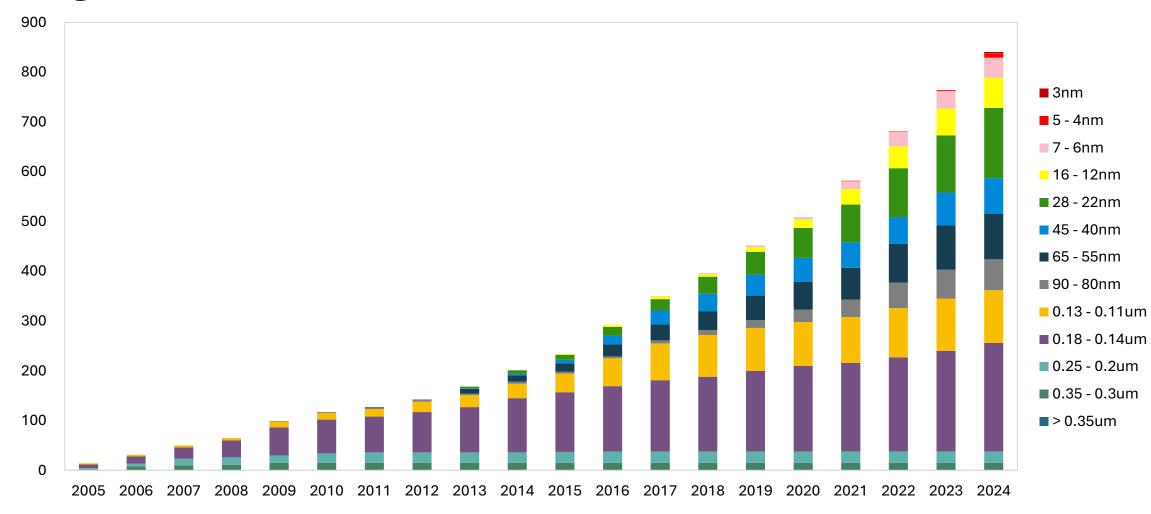

#### Registered IPs at TSMC -

#### **Registered IP > 750**

page 5

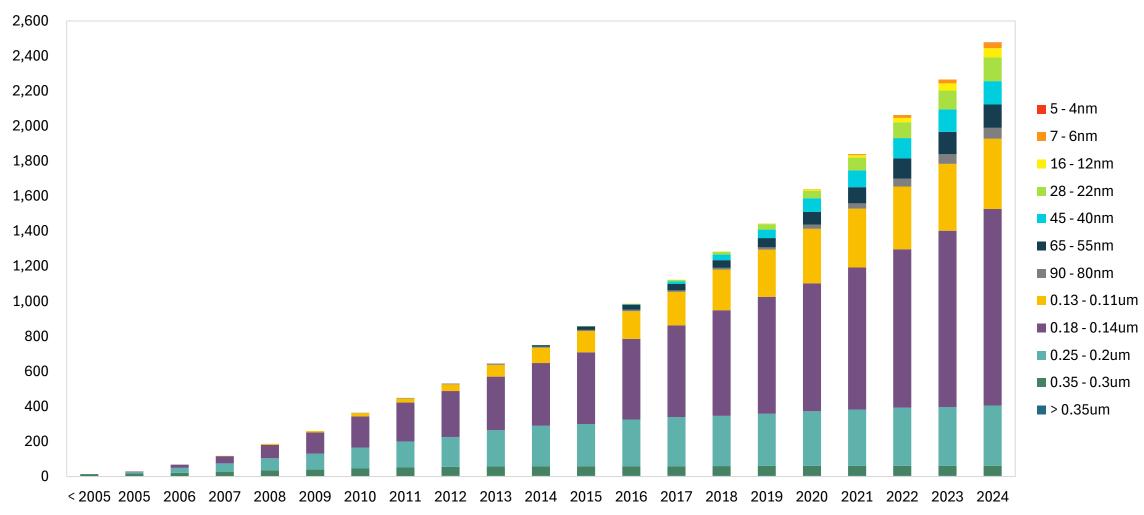

#### NTOs at TSMC .

#### **New Tape Out Contribution > 2400**

#### Wafer Contribution at TSMC \_

#### 8" Wafer Contribution > 25M

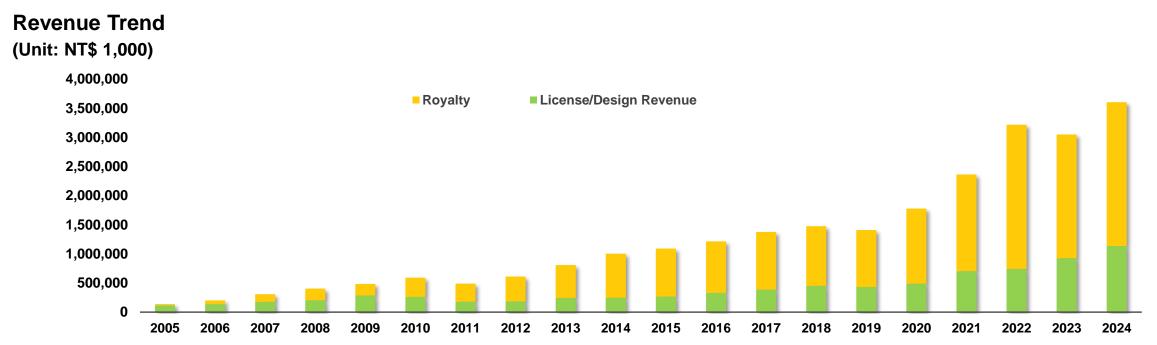

#### Revenue and Tape-out by Technology \_

|       | NTO    |         | Revenue (USD)     |    |             |    |            |

|-------|--------|---------|-------------------|----|-------------|----|------------|

| Year  | NeoBit | NeoFuse | NeoBit            |    | NeoFuse     | Р  | UF-based   |

| 2002  | 3      |         |                   |    |             |    |            |

| 2003  | 29     |         |                   |    |             |    |            |

| 2004  | 40     |         |                   |    |             |    |            |

| 2005  | 68     |         | \$<br>4,217,380   |    |             |    |            |

| 2006  | 133    |         | \$<br>6,202,270   |    |             |    |            |

| 2007  | 220    |         | \$<br>9,402,479   |    |             |    |            |

| 2008  | 253    |         | \$<br>12,896,211  |    |             |    |            |

| 2009  | 268    |         | \$<br>11,695,587  |    |             |    |            |

| 2010  | 284    |         | \$<br>15,873,331  |    |             |    |            |

| 2011  | 254    |         | \$<br>15,399,098  |    |             |    |            |

| 2012  | 270    |         | \$<br>19,620,768  |    |             |    |            |

| 2013  | 363    | 1       | \$<br>25,436,669  | \$ | 382,084     |    |            |

| 2014  | 371    | 3       | \$<br>31,831,985  | \$ | 328,787     |    |            |

| 2015  | 311    | 11      | \$<br>30,943,426  | \$ | 1,080,373   |    |            |

| 2016  | 270    | 28      | \$<br>30,247,340  | \$ | 3,636,142   |    |            |

| 2017  | 257    | 61      | \$<br>34,619,653  | \$ | 5,238,351   |    |            |

| 2018  | 253    | 86      | \$<br>31,834,860  | \$ | 10,773,223  | \$ | 85,000     |

| 2019  | 226    | 109     | \$<br>27,602,332  | \$ | 14,466,279  | \$ | 195,000    |

| 2020  | 248    | 182     | \$<br>30,378,346  | \$ | 26,437,660  | \$ | 434,998    |

| 2021  | 252    | 259     | \$<br>32,367,560  | \$ | 44,011,223  | \$ | 1,160,702  |

| 2022  | 264    | 231     | \$<br>35,327,060  | \$ | 63,762,480  | \$ | 4,207,209  |

| 2023  | 226    | 241     | \$<br>23,251,721  | \$ | 64,276,058  | \$ | 4,375,409  |

| 2024  | 266    | 270     | \$<br>25,952,137  | \$ | 71,649,123  | \$ | 5,279,985  |

| Total | 5,129  | 1,482   | \$<br>455,100,213 | \$ | 306,041,783 | \$ | 15,738,303 |

\*NTO stands for **New Tape-Out**

\* Revenue includes both licensing and royalty

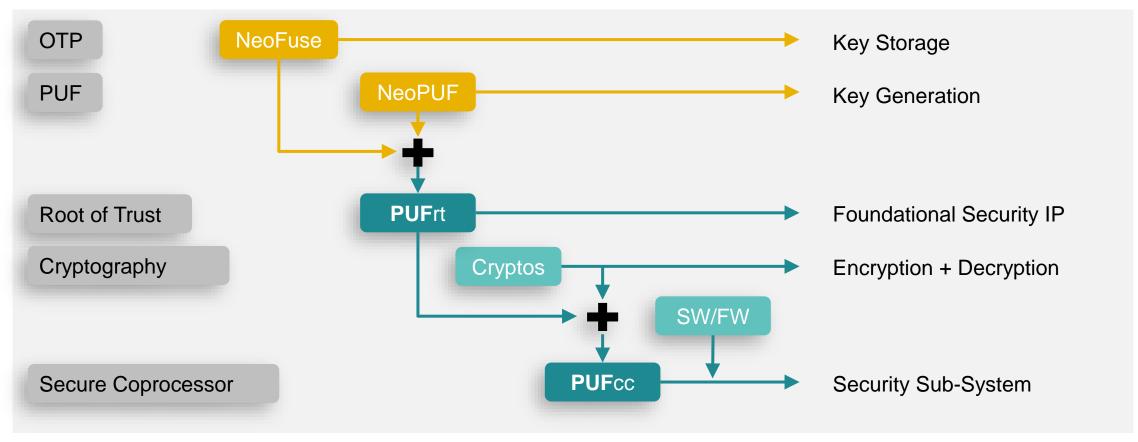

#### PUF-based Security Solutions \_

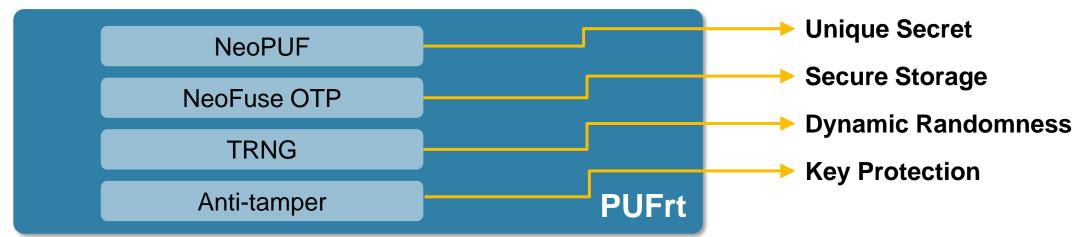

- Based on OTP Technologies, many different security functions IPs have evolved

- Regulations, such as TPM 2.0, now require Hardware Root of Trust

#### Standards Drive Hardware-Based Security .

#### Driving an open standard for silicon root of trust

Using asymmetric public/private key encryption technology and device ID to achieve fast and secure access to the network

Confidential

#### Security Business Development

As eMemory is an established IP company, there are different platforms that we can leverage for sales in security IPs and sub-systems

#### **Foundry Platforms**

TSMC, Intel, UMC, GF, etc.

- Licensed our security technology to major foundries

- Co-promotional activities

#### **CPU Partners**

Arm, RISC-V, Cadence, etc.

SoC customers looking for both CPU and security subsystems

**CSP**

#### More to come

- Work with CSP and system companies for embedded security on a chip level

#### Market Application

Customers with many different applications will begin to adopt PUF-based Security Solutions

| CPU  | AI      | SSD       |

|------|---------|-----------|

| DPU  | DTV/STB | Wi-Fi     |

| FPGA | ISP     | And More. |

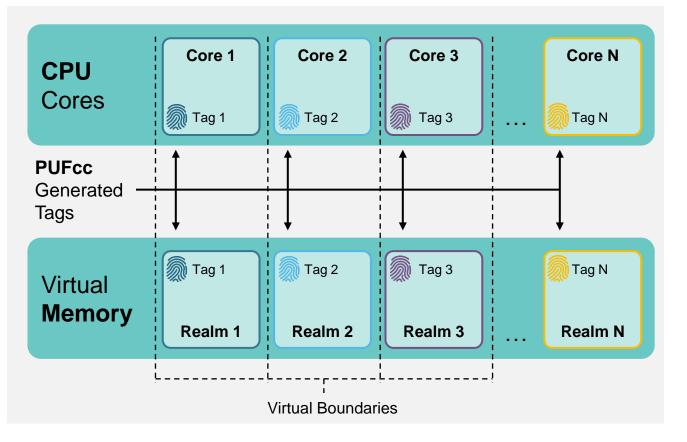

#### Next Computing: Confidential Computing -

- Protect data in the Virtual Memory of Multi-Core CPUs

- CPU Cores and Virtual Memory have unique corresponding tag numbers

- Tag numbers are internally randomly generated by PUFcc (Crypto Coprocessor IP)

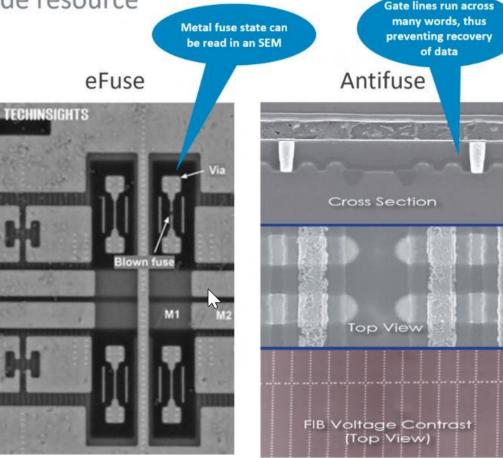

### AntiFuse OTP vs. eFuse

#### One Time Programable (OTP) memory is a SoC-wide resource

- RSS supports OTP as field-programmable to store confidential code and data

- eFuse:

- Area efficient for smaller arrays

- Typically not field programmable

- Can be easily read by delayering SoC (a few \$k cost)

- The secure channel key can be compromised

- The device can then be cloned

- Antifuse OTP:

Confidential © 2021 Arm

- Cannot be read using a scanning electron microscope

- Dense bit cells, efficient for large arrays

- Macro periphery is large versus eFuse

- Integrated charge pump enables field programming

- · PUF can be included for a small additional area

- ~0.04mm2 on 7nm for 128x32 bit PUF

https://semiengineering.com/the-benefits-of-antifuse-otp/

Rainer Herberholz

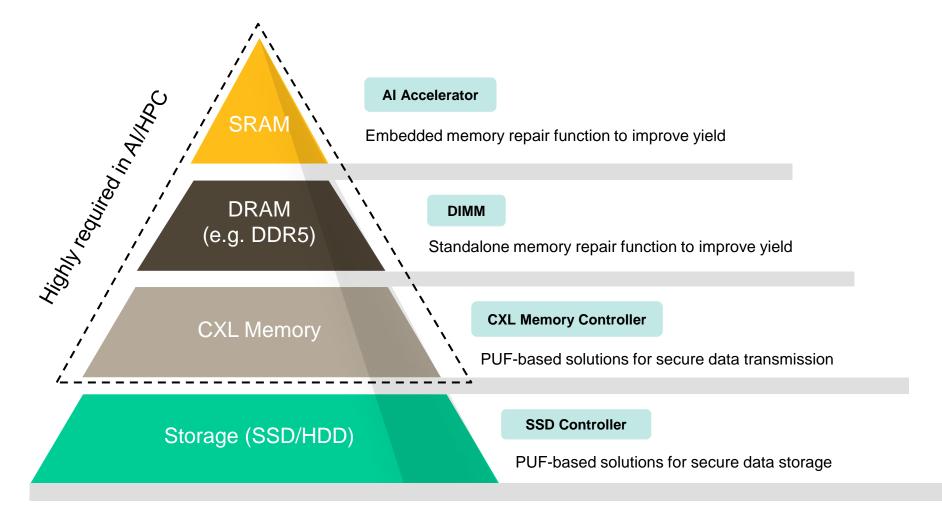

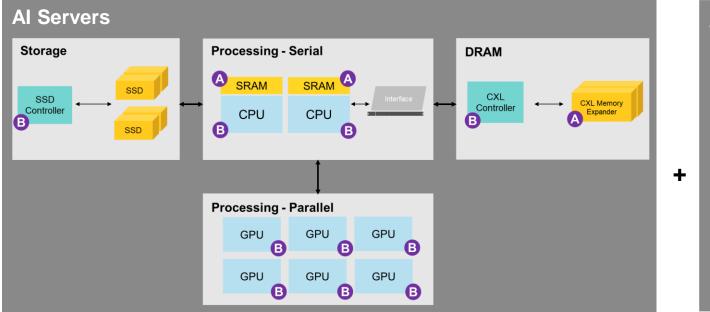

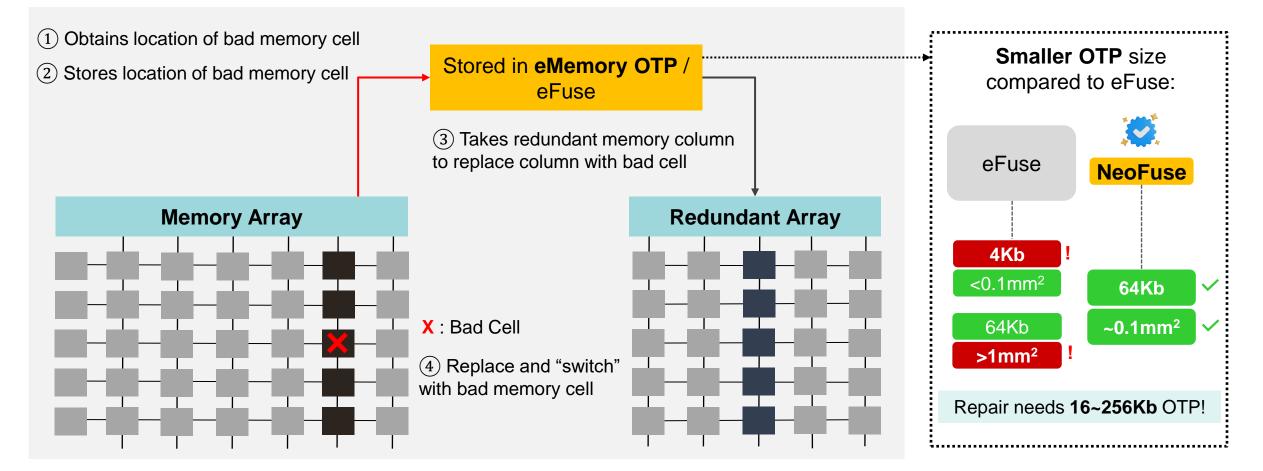

### Example: eMemory Helps Memory\_

eMemory's security IP and OTP/MTP IP 1) ensure data security and 2) improve yield for SRAM and DRAM.

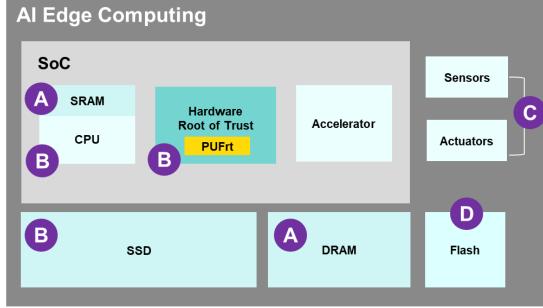

#### eMemory for AI Servers and Edge Devices

A Memory Repair

- **B** Root of Trust provides:

- 1. Key storage/generation

- Cryptographic processing to protect AI models, input data and output results

- 3. Confidential Computing

**OTP** needed for trimming analog circuits in Sensors and Actuators **NeoFlash** to replace conventional eFlash for a much lower cost

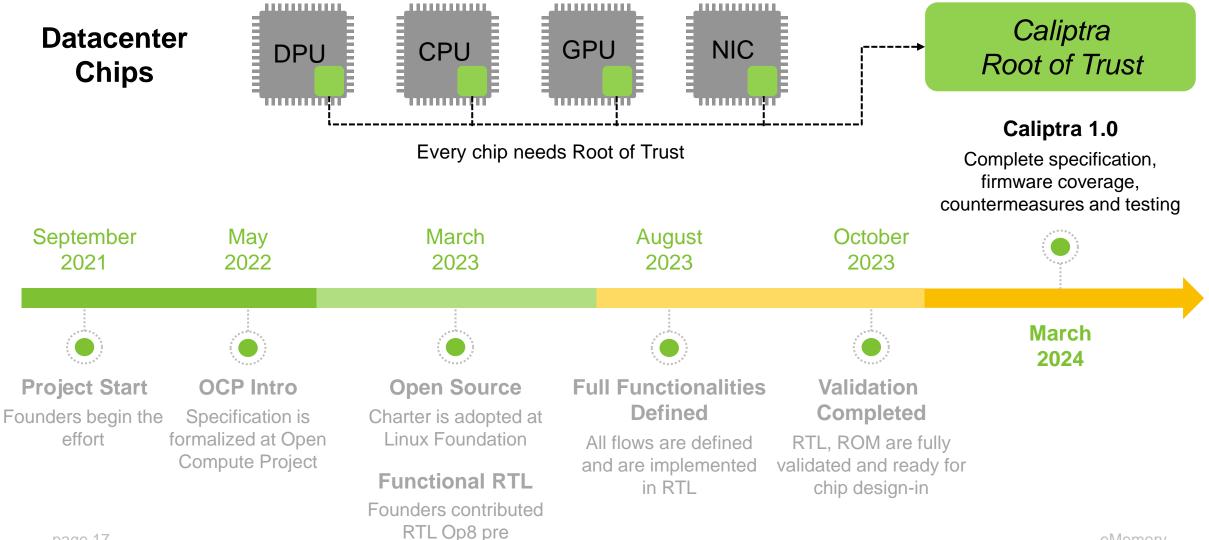

#### Why is **Caliptra** so Important?

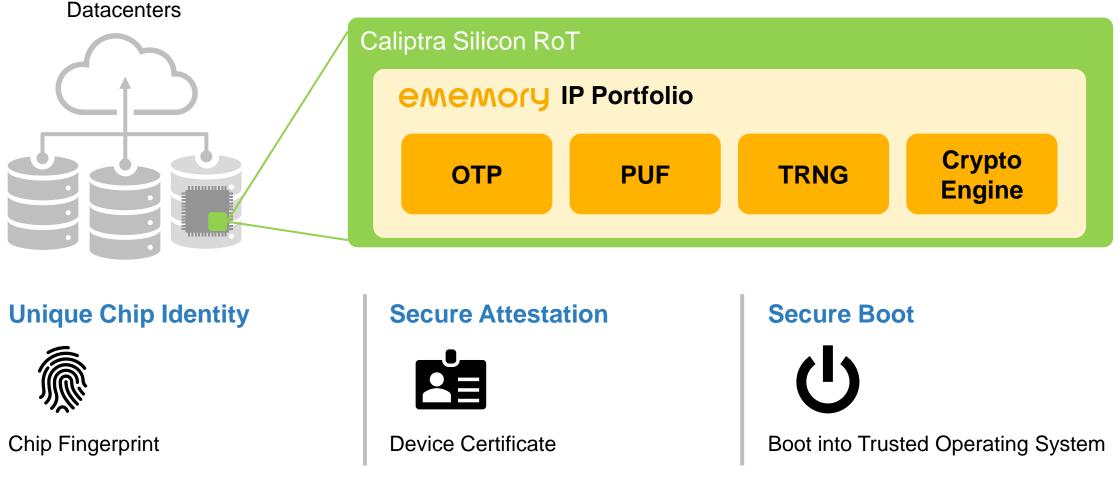

### What is the Important Role of eMemory in Caliptra?

eMemory's root of trust IP is ready to meet Caliptra's requirements.

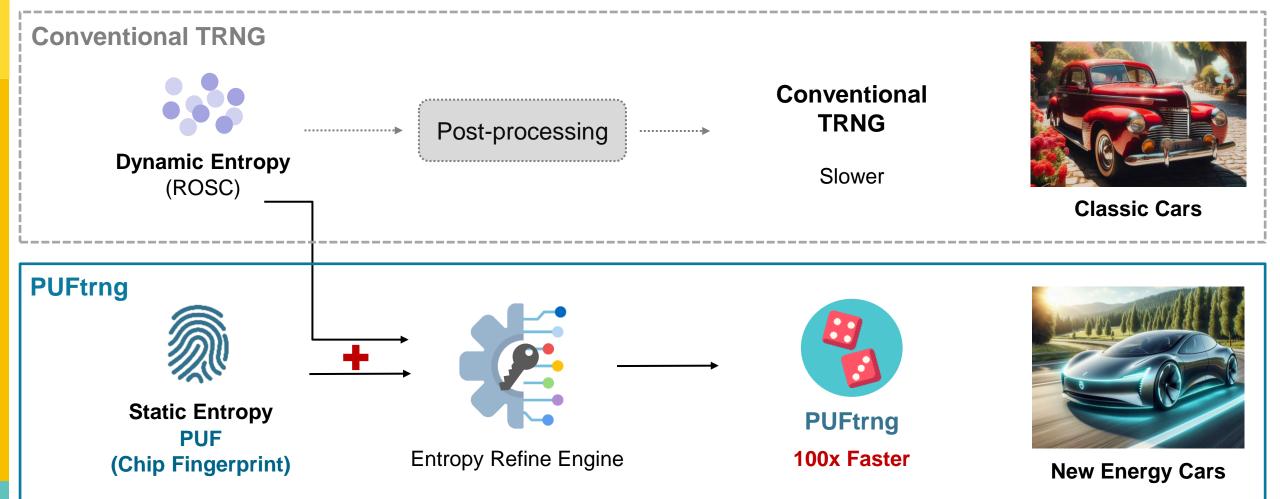

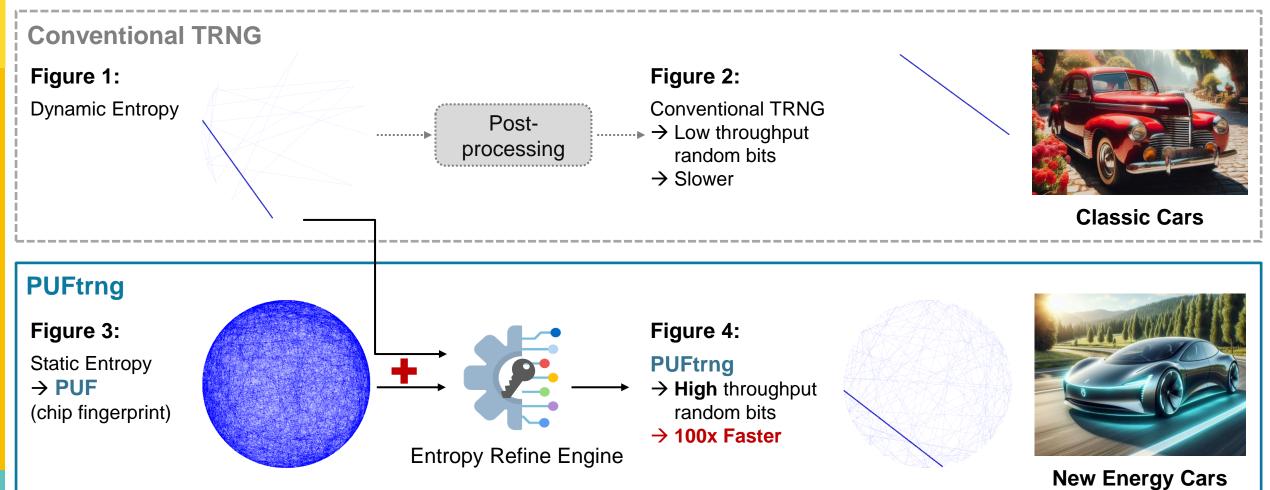

### PUFtrng: 100 Times Faster than Conventional TRNG

PUF-based conditioning algorithm provides high-throughput and high entropy quality

Similar to ...

# **PUFtrng:** 100 Times Faster than Conventional TRNG

PUF-based conditioning algorithm provides high-throughput and high-quality entropy

Similar to...

# Why is High-Density SRAM needed in AI?

To increase the speed of AI accelerators, **high-density SRAM** is needed for use in:

| Buffer Memory                                                                                                                                                                                         | AI Model Training                                                                                                                                  | Computing in Memory<br>(CIM) for Inference                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>High-density SRAM helps<br/>improve data transfer<br/>speed and reduce energy<br/>costs by acting as a fast<br/>intermediate storage<br/>between different<br/>processing stages.</li> </ul> | <ul> <li>High-density SRAM helps<br/>store vast amounts of data<br/>for AI accelerators to<br/>access quickly to speed up<br/>training.</li> </ul> | <ul> <li>High-density SRAM<br/>enables in-memory<br/>computation by storing<br/>large datasets and<br/>performing computations<br/>on them without<br/>transferring data to<br/>separate processors.</li> </ul> |

## eMemory enables High-Yielding SRAM

SRAM yield decreases as technology is scaled due to smaller dimensions. To increase yield, eMemory's OTP is required.

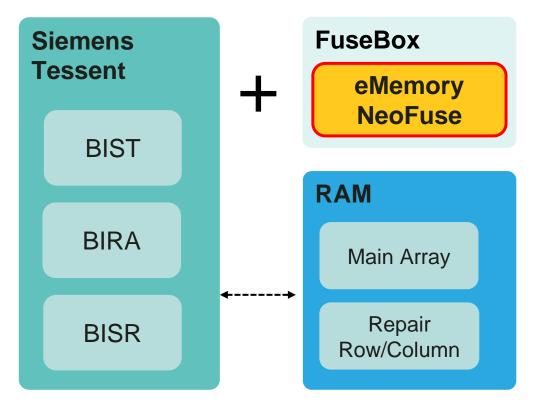

### Partnering for Success: eMemory and Siemens

BIST = Built-in Self Test BIRA = Built-In Redundancy Analysis BISR = Memory Built-in Self Repair eMemory provides OTP with interface for Siemens MBIST:

- Tessent provides memory BISR functions with BIST and BIRA

- NeoFuse OTP provides defect-free OTP using BIRA, BISR and adapter to Tessent

- New MBISR: Tessent MBISR + NeoFuse, scann ing defective SRAM by word/column and loggin g to the OTP

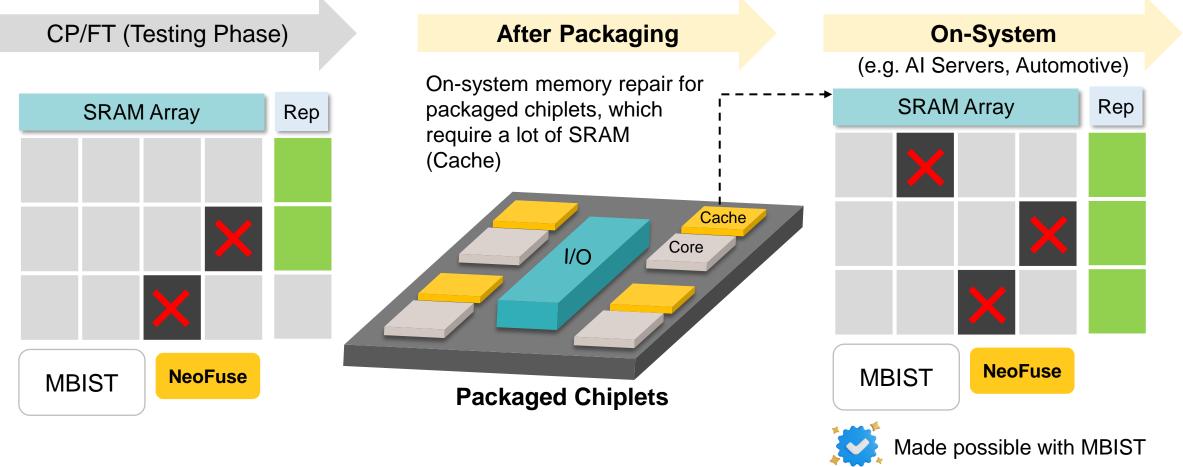

# On-System Repair for AI Accelerators

eMemory

Memory Built-in Self-Test (MBIST) offers on-system repair capabilities, which are essential for high-speed high-reliability applications and chiplet architecture or after system packaging.

### eMemory enables HPC in Al Applications

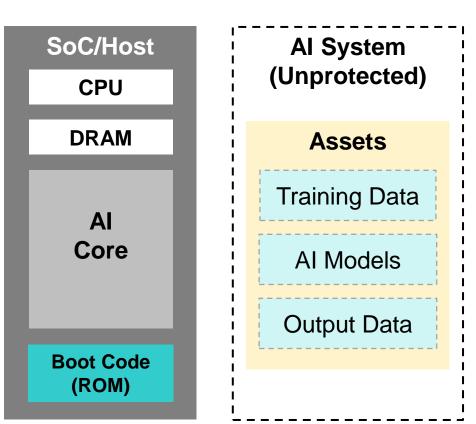

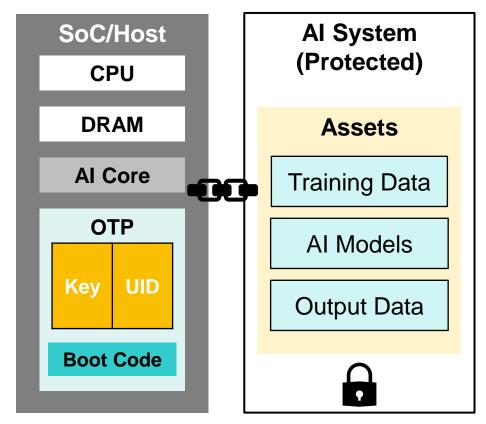

eMemory's OTPs can also store boot codes, root key and unique ID for the root of trust in AI systems.

#### Without eMemory OTP

With eMemory OTP

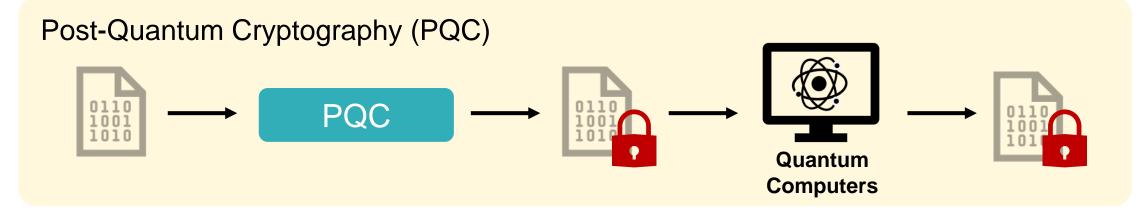

#### Why PQC Needs PUF?

**PUF** can **efficiently generate keys with long length**, which is needed for PQC.

**PUF** can **efficiently provide random numbers**, which are needed for **anti-tampering** in PQC.

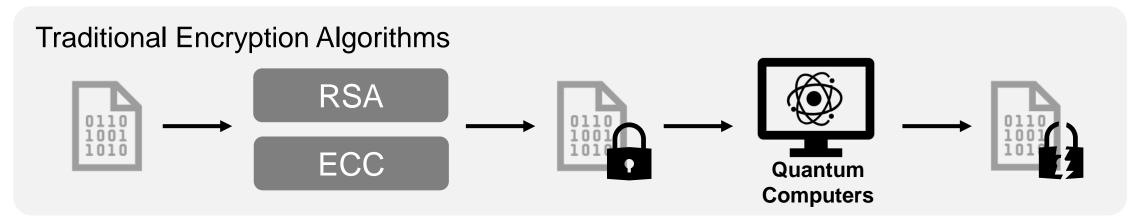

#### What is **PQC?**

PQC aims to create cryptographic systems that can withstand attacks from quantum computers.

### Why is **PQC** Needed?

- As quantum computing progresses, the demand for encryption capable of resisting quantum attacks becomes critical.

- The sooner we implement PQC, the sooner we can guarantee the security of our data in a quantum future.

| Implement PQC Now                              |     | <u>Safeguard our data</u><br>in the Quantum Future | 2   |

|------------------------------------------------|-----|----------------------------------------------------|-----|

| Financial Transactions<br>Personal Information |     | Financial Transactions<br>Personal Information     |     |

| Sensitive Government Data                      | PQC | Sensitive Government Data                          | PQC |

- In 2024, NIST officially announced three standards for PQC:

- FIPS 203, Module-Lattice-Based Key-Encapsulation Mechanism Standard

- FIPS 204, Module-Lattice-Based Digital Signature Standard

- FIPS 205, Hash-Based Digital Signature Standard

#### How PUF-based Solutions Help PQC?

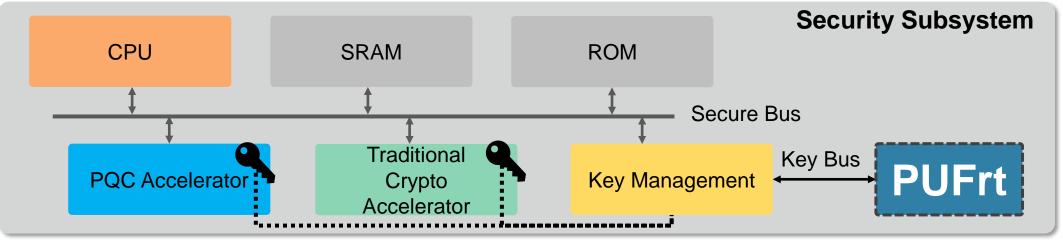

• Our PUF-based Root of Trust (PUFrt) can help PQC:

By integrating the PUFrt into the security subsystem, it can effectively manage the long and complex keys required for PQC algorithms.

# Thank You for your time

For more information, please visit: eMemory Website: <u>https://www.ememory.com.tw/</u> PUFsecurity Website: <u>https://www.pufsecurity.com/</u>

# ememory